全球15家AI芯片公司同時現(xiàn)身市場, 這是15年來半導體行業(yè)從未有過的奇景

編者按:本文來自機器之能(ID:almosthuman2017),編譯:王宇欣、陳韻竹、Rik R,編輯:宇多田,來源:EE Times。36氪經授權轉載。

對于人類社會,深度神經網絡就像是那遙遠地平線上出現(xiàn)的海嘯一般。

鑒于它們的算法和應用目前仍在不斷演變,所以尚不清楚深度神經網絡(DNNs)最終將會帶來怎樣的變化。

但是,迄今為止,它們在文本翻譯和圖像、語音識別領域取得的成功讓我們認識到,深度神經網絡終有一日將會重塑計算機設計,而這樣的變化對半導體設計和制造領域也同樣有著深遠的影響。

為 DNNs 量身定制的第一批商用芯片將于今年上市。鑒于它能夠用幾星期或幾個月時間來訓練一個新的神經網絡模型,這些芯片可能是迄今為止制造規(guī)模最大的,因此也可能是成本最高的商用芯片。

今年,這個行業(yè)會看到 Graphcore 公司開發(fā)的一款非 Dram 模式的微處理器,以及其競爭對手——在圓片級芯片封裝技術方面較為領先的 Cerebras Systems 也會推出一款產品。

與此同時,英特爾收購的 2.5-D Nervana 芯片已經開始取樣,其他諸多廠商的芯片研發(fā)也都在火熱進行當中。

此外,從 ARM 到西部數(shù)據(jù)(Western Digital),所有老牌半導體巨頭也均在研究處理器核心以加速深度神經網絡的推理部分。

「我認為 2018 年,將會是各種芯片產品『百家爭鳴』的一年。我們開始見到許多公司正在評估各種針對芯片的 idea,」加州伯克利榮譽教授 David Patterson 如是說道。

這個趨勢相當明顯,Patterson 與聯(lián)合作者 John Hennessey 在上個月出版的 Computer Architecture(在計算領域影響巨大)一書的最新版本中,用整整一個章節(jié)介紹了這種趨勢。

作者對一些內部設計給出了深度的見解,譬如 Patterson 對谷歌的TensorFlow Processor(TPU),微軟的 Catapult FPGA,以及蘋果與 Google 最新的手機芯片中的推理模塊都給出了自己的意見。

Patterson 表示:「這是計算機架構與封裝技術的復興。在明年一年我們將會看到比過去十年更多的,更有意思的計算機出現(xiàn)?!?

在過去幾年中,深度神經網絡的興起將風投的資金重新帶回到半導體的領域。

在電子工程師時報(EE Times)最新發(fā)布的「Silicon 60」中,他們列出了 7 家致力于研究新型神經網絡芯片的初創(chuàng)公司,其中包含了兩個不太為人所知的公司:

北京的寒武紀科技與美國德克薩斯州的 Mythic Inc。

Chris Rowen 從 Cadence Design Systems 離職后,成立了一家名為 Cognite Ventures 的投資公司,專門看神經網絡軟件。

「我們看到具備全新架構的新創(chuàng)業(yè)公司如井噴式出現(xiàn)。我自己追蹤了 15 到 20 家公司…在過去的 10 ~15 年時間里,在任何半導體子領域里都不曾有過『同時出現(xiàn) 15 家半導體公司』這樣的事情。」Chris Rowen 說道。

他表示:「由于英偉達難以撼動的軟件地位,與其在高階服務器訓練方面的競爭將會十分艱難;

而如果你去追求手機市場,那你一定是瘋了,要知道追求手機市場意味著你必須在很多方面都做得出色。不過在高階或是低階的手機市場中,還可能有一些機會。」

市場觀察者 The Linley Group 的負責人 Linley Gwennap 表示,英偉達最新的 GPU—Volta 性能非常不錯,他們對其進行了調整以進行 DNNs 的速度訓練。但 Gwennap 卻不認為 Volta 就是最好的設計。

Gwennap 說,Graphcore(英國布里斯托)和 Cerebras(加州洛杉磯)是在訓練芯片方面最值得觀察的兩家公司,他們籌集了最多的資金,而且似乎擁有最好的團隊。

此外,由谷歌前芯片設計員創(chuàng)立的初創(chuàng)公司 Groq 聲稱將會在 2018 年推出一款推理芯片,每秒的運算和推理都能完勝對手 4 倍。

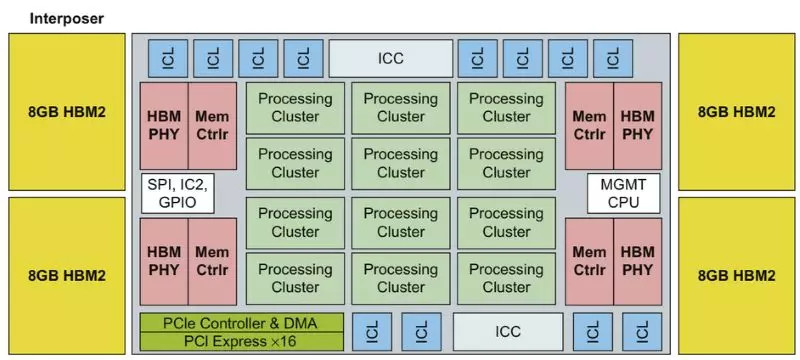

英特爾的 Nervana 是一個大型的線性代數(shù)加速器,位于一個硅中介層上,緊鄰著四個 8GB 的 HBM2 內存棧英特爾的 Nervana,被稱為 Lake Crest(上圖),是最受關注的定制設計之一。Nervana 使用數(shù)據(jù)共享指令集中提供的單個 5 位元指數(shù),執(zhí)行 16 位矩陣操作。

與英偉達的 Volta 一樣,Lake Crest 的邏輯單元位于一個 TSMC CoWoS 中介層上(芯片-晶片-基板),緊鄰著四個 HBM2 高頻寬內存棧。

這些芯片被設計成網狀,是 Volta 性能的 5~10 倍。

雖然去年微軟在 DNN 上使用了 FPGA,但是 Patterson 仍然對這種方法持懷疑態(tài)度?!改銥?FPGA 的靈活性付出了很多的代價;編程真的很困難,」他說。

Gwennap 在去年年底的一項分析中指出,DSP 也將會發(fā)揮作用?!窩adence、Ceva 和 Synopsys 都提供面向神經網絡的 DSP 內核」。

AI芯片即將到來,而架構師還未決定如何對其進行評估。

就像 RISC 處理器的早期那樣,Patterson 回憶道:「每一家公司都會說,『你可千萬不能相信別人的基準體系,但是你可以相信我的』,這可不太好?!?

時間退回到那時候,當時 RISC 供應商在 SPEC 基準測試中進行了合作?,F(xiàn)在 DNN 加速器需要定義自己的測試組件,涵蓋各種數(shù)據(jù)類型的訓練、推理。

為了順應這種趨勢,12 月 12 日,由 20 多家頂級服務器和軟件制造商組成的交易處理性能委員會(TPC)宣布組建一個工作組對機器學習的硬件和軟件基準進行定義。

TPC - AI 委員會主席 Raghu Nambiar 表示,這個工作組的目標是要創(chuàng)建出對 CPU 和 GPU 加速器通用的測試。但是,團隊成員名單和時限仍未最終確定。

百度,于 2016 年 9 月發(fā)布了一個基于深度學習工作負載的開源基準,使用 32 位浮點數(shù)執(zhí)行訓練任務。它在六月份更新了 DeepBench 以涵蓋推理工作并使用 16 位制。

美國哈佛大學的研究人員發(fā)表的 Fathom 套件,定義了 8 個人工智能工作負載,支持整數(shù)和浮點數(shù)據(jù)。Patterson 說:「這是一個開始,但是要成為一個讓人滿意的全面基準測試套件,還有很多的工作要做。」

「如果我們致力于建立一個好的基準,所有投入工程的錢都會花在刀刃上?!?

除了基準之外,工程師需要持續(xù)追蹤不斷變化的神經網絡算法,從而確保他們的設計能跟上時代。

高通公司下一代核心(next-generation-core)研發(fā)總監(jiān) Karam Chatha 表示:

「軟件正在不斷變化,但是我們需要盡早把硬件拿出來,因為硬件會影響軟件——軟硬件之間總會有這樣相互牽連的關系?!?

到目前為止,這家移動芯片供應商仍在驍龍?zhí)幚砥鞯?DSP 和 GPU 內核的軟件平臺上進行神經網絡運行工作。

但是一些觀察人士預計,高通將為機器學習定制一個全新的模塊。在 2019 年,該模塊將成為驍龍?zhí)幚砥髦幸粋€大約 7 豪微米的部分。

高通展示了一個 DNN 定制加速器研究實例,但現(xiàn)在,高通在使用通用 DSP 和 GPU 內核上的軟件

Patterson 表示:「市場是芯片質量的檢驗者。這很殘酷,但也正是計算機設計讓人興奮的地方?!?

實際上,早期的芯片玩家已經抓住了這次競爭的機遇。

舉例來說,F(xiàn)acebook 最近證明,通過大幅增加所謂批量尺寸(batch size)中的特征數(shù)目,能將某些任務的訓練時間從一天縮短到一小時。

但這對于芯片制造商 Graphcore 而言可能是個壞消息。因為 Graphcore 試圖將所有操作放在本地 SRAM 中運行,以消除外部 DRAM 的訪問延遲,但與此同時也會限制其內存占用。

Patterson 說道:「Graphcore 專為小批量設計,但是幾個月前軟件結果表明,大批量尺寸效果更好。事情總是瞬息萬變。」

另一方面,Rex Computing 認為他們正好抓住了有利的機遇。該初創(chuàng)公司的 SoC 最初為高性能服務器設計,其中使用了一種新型暫存器內存。

Rex Computing 聯(lián)合創(chuàng)始人 Thomas Sohmers 表示,Rex 的方法消除了在虛擬頁表中對數(shù)據(jù)緩存的需求,這是一種在 GPU 中使用的技術,能增加延遲。

因此,Thomas Sohmers 說,尤其在處理當下神經網絡中流行的矩陣運算和矢量運算時,Rex 芯片性能遠勝于現(xiàn)在的 GPU。

該初創(chuàng)公司計劃于 6 月份推出 256 核的 16-nm SoC,希望其能效比能達到 256 Gflops/W。

與此同時,研究人員正在嘗試單比特浮點數(shù)、 32 比特浮點數(shù)以及整型等各種精度的計算,旨在尋找神經網絡計算中效率最高的方法。

看起來他們在某一點上達成了一致,即不要在不同的精度等級間進行轉換。

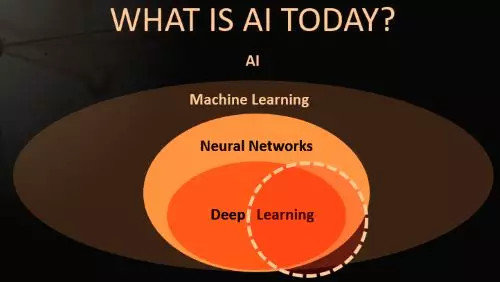

幾十年來,深度神經網絡一直是人工智能領域中的一個小分支。

自 2012 年左右開始,包括 Facebook 的 Yann LeCun 在內的研究人員開始使用特定種類的 DNN 進行圖像識別,最終獲得了比人類更高的準確率,顯示出驚人的成果。

深度學習技術吸引了學界,現(xiàn)在學術圈正在高速發(fā)表論文,尋求新的突破。

如今,DNN 正在提供商業(yè)化服務,如亞馬遜的 Alexa 、谷歌翻譯、Facebook 面部識別等。網絡巨頭和全球其他競爭者正競相將這些技術應用于各種服務中,盡其所能尋找殺手級應用。

微軟每年都會在人工智能方面主持兩場僅員工參與的會議。前 SPARC 處理器架構師 Marc Tremblay 表示,上一場會議有 5000 人參加。Marc Tremblay 現(xiàn)在正帶領微軟進行 AI 專用芯片和系統(tǒng)方面的工作。

專家們承認,他們并不完全理解現(xiàn)有算法為何能得到良好的效果。

這質疑了 DNN 及其他各類模式的相對有效性,例如循環(huán)神經網絡(RNN)和卷積神經網絡(CNN)等。與此同時,學者還在不斷發(fā)明新的模式。

「算法在五年內會發(fā)生變化的可能性很高。我們正在進行一場賭博——像矩陣乘法這樣的最底層東西是不可改變的?!乖谧罱P于人工智能的 IEEE 研討會上,AMD 公司研究員 Allen Rush 這樣說。

這就是 Google 用 TPU 做的賭注。

最新版本的 TPU 是能同時針對訓練和推理工作。本質上說,TPU 是一個巨大的乘加單元陣列,對矩陣操作進行運行和存儲。預計 Nervana 和 Graphcore 的芯片將效仿這一模式。

哈佛大學前大腦研究員、Nervana 的聯(lián)合創(chuàng)始人 Amir Khosrowshahi,目前正在英特爾 Nervana 集團任首席技術官。

他說,目前在神經網絡方面取得的成功占據(jù)了人工智能領域成果的絕大部分。他在 IEEE 研討會上表示:

「由于深度學習的極大成功,我們對很多領域都避而不談。當下,人人都在研究 CNN,這是一場悲劇……不要以為現(xiàn)在的熱潮會一直持續(xù)到明年?!?

如今的 DNN 受到了極大的關注,但是它只代表人工智能廣泛領域中的一小部分

盡管 DNN 在圖像識別方面比人類有著更高的精確率,「但如今的數(shù)據(jù)科學家不得不花費過長的時間對數(shù)據(jù)進行預處理,對模型和參數(shù)進行迭代,并且等待訓練收斂……其中,每個步驟要么有著過于密集的勞動,要么有著過于密集的計算量」,Khosrowshahi 說道。

總而言之,他補充說:「人工智能領域仍面臨著許多難題。頂尖研究者能讓機器人打開一扇門,但是讓機器人端起茶杯可能比打敗 AlphaGo 困難得多?!?

在這種環(huán)境下,F(xiàn)acebook 和 Google 等網絡巨頭正在發(fā)布大量的數(shù)據(jù)集,讓更多的人從事前沿問題,例如將識別應用于視頻等新興領域或其他數(shù)據(jù)類型。

隨著算法的不斷發(fā)展,研究人員也在拓展深度學習的應用邊界。

谷歌致力于將深度神經網絡系統(tǒng)性地應用于一系列問題,比如為盲人用戶自動添加圖片說明文字、解讀核磁共振成像的掃描結果,以及輔助工廠的質量控制監(jiān)督工作。

「人工智能并非一種單一的技術或產品,」谷歌研發(fā)部負責人李佳告訴 IEEE 研討會,「我們需要先理解那個領域,然后收集數(shù)據(jù)、找出適配算法并提出解決方案。每一個新問題都需要一個不同的模型?!?

事實上,業(yè)界正在將深度神經網絡系應用于幾乎任何領域,包括芯片的設計與制作。英特爾列出了 40 多個可能的應用方向,從消費者在線購物助理,到華爾街自動交易程序。

現(xiàn)任 Target 數(shù)據(jù)科學家的 Shirish Tatikonda,曾在 IBM 做研究員,對深度神經網絡的應用邊界有著更加清醒的認識。

他在一次簡短的采訪中談到,零售商的大多數(shù)數(shù)據(jù)都是有關聯(lián)的,不是那種最適合于神經網絡的非結構化類型;在 Target 所接手的業(yè)務問題中,只有 10% 適用于深度神經網絡。

盡管如此,Target 公司仍在積極探索該領域,其大約 10% 的系統(tǒng)使用的是 GPU 服務器,用于訓練神經網絡模型。

為了實現(xiàn)規(guī)?;雀璧难芯咳藛T正致力于探究被其稱為 AutoML 的軟件。其思想是使用神經網絡來自動生成模型,無需數(shù)據(jù)科學家對其進行手動調整。

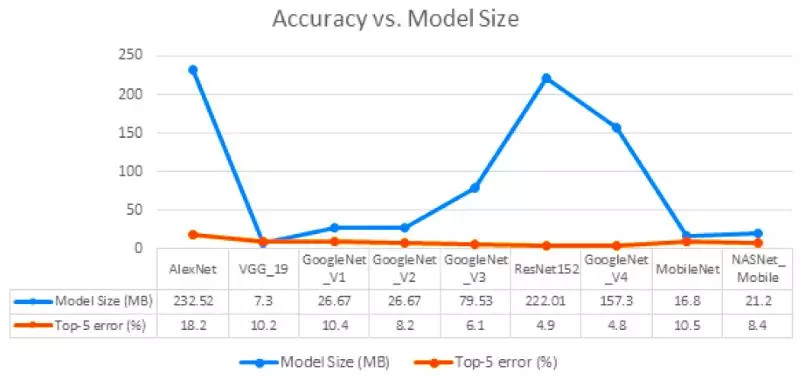

雖然近年來有許多研究人員尋求減少深度神經網絡模型的內存占用,但其尺寸差異仍然十分巨大

機器人先驅 Rodney Brooks 擔心,業(yè)界對這種算法的預期可能過于樂觀了。他在最近的一次談話中說:「深度學習很好,但它正被當成萬靈藥?!?

就 Patterson 而言,他仍然選擇保持樂觀。雖然廣博的人工智能領域沒有兌現(xiàn)過去的一些承諾,但它在機器翻譯等領域所取得的成功卻是真實的。

「你可以說好采的果子都被采完了,不會再有更令人興奮的事情了,但事實上幾乎每周都會出現(xiàn)新的進展...... 所以我想我們會發(fā)現(xiàn)更多的用途。」

深度學習的早期發(fā)展充溢著狂熱與碎片化,即使軟件融合工作都被搞得支離破碎。

百度的人工智能研究小組進行了一項調查,提出 11 項舉措來彌合不同神經網絡管理軟件框架之間的隔閡。

Facebook、微軟以及新近加入的亞馬遜發(fā)起了一個比較靠譜的開源解決方案,叫做開源神經網絡交換(Open Neural Network Exchange,ONNX)。

該項目在 12 月發(fā)布了 ONNX 的 1.0 版。其目標是將軟件框架領域的 12 家競爭廠商所創(chuàng)建的神經網絡模型轉化為一種圖形表示。芯片制造商可以使用這種圖形表示來進行硬件開發(fā)。

對于初創(chuàng)企業(yè)來說,無論是亞馬遜的 MxNet 或谷歌的 TensorFlow,還是 Facebook 的 Caffe2 或微軟的 CNTK,這些競爭廠商所編寫的模型框架都很難互相兼容,而它們也無力編寫單獨的軟件,ONNX 無疑是一個福音。

12 月 20 日,由 30 多個主要的芯片廠商組成的一個研究小組發(fā)布了他們的首選方案——神經網絡交換格式(Neural Network Exchange Format,NNEF)。

NNEF 旨在為芯片制造商提供一種個性化的選擇,使他們能夠創(chuàng)建屬于自己的、供內部員工使用的格式,比如英特爾的 Nervana Graph 和英偉達的 TensorRT。

百度創(chuàng)建的格式有 ISAAC、NNVM、Poplar 和 XLA。

「置于哪一個將被成功實施,現(xiàn)在還不好說,但我們正在穩(wěn)步前進,而最終一定會有一個從中脫穎而出,」百度的硅谷人工智能實驗室高級研究員 Greg Diamos 說道。

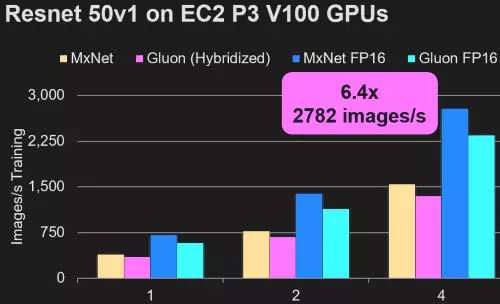

在人工智能框架方面,亞馬遜聲稱其 MxNet 框架及其新開發(fā)的 Gluon API 效率最高

另外,谷歌已經開始致力于自動化深度神經網絡模型的簡化過程,以便在智能手機、物聯(lián)網(IoT)節(jié)點等任何平臺上運行。

如果該項目成功的話,可以將 50 兆字節(jié)的模型縮小到只有 500 字節(jié)。

谷歌也在探索如何在手機端進行有限模型訓練,其方法是調整模型的頂層網絡,或是在白天收集數(shù)據(jù),然后在夜間運行流程。

同樣,SqueezeNet 和 MobileNet 等業(yè)界同行也在開發(fā)類似的成像模型,精度與其科技界的大表哥們不相上下。

「我們已經看到,機器學習正被大量應用在五花八門的產品中,」谷歌的 TensorFlow Lite 負責人 Pete Warden 說道,「支持我徹夜工作的動力,就是能夠降低一絲一毫的運算能耗?!?

當專家們專注于探索人工智能的未來時,他們看到了一些有趣的可能性。

目前,我們所使用的有監(jiān)督學習是基于手動調整。

Warden 是谷歌的一名研究人員,他和同事們都認為,不久的將來會出現(xiàn)一些半監(jiān)督的學習方式,例如手機等客戶端設備可以獨自處理一些學習任務。

而最終的目標是無監(jiān)督學習——即計算機自學,無需工程師的幫助。

一直以來,研究人員都希望能夠尋找出一種方法,使手機或物聯(lián)網節(jié)點等設備在收集數(shù)據(jù)時可以自動對其進行標記。

「谷歌認為,在這個中間階段,我們現(xiàn)在需要進行大量的計算,但是一旦可以自動標記數(shù)據(jù),你就只需要索引新的增量內容,這更像是人類的數(shù)據(jù)處理方式,」Western Digital 首席數(shù)據(jù)科學家 Janet George 說道。

無監(jiān)督學習打開了一扇通往加速機器智能時代的大門,有些人將其看作是數(shù)字天堂。

而另一些人則擔心,缺少人為干預的技術可能會失控,從而帶來災難性的后果?!高@就是我害怕的地方,」處理器領域資深老兵 Norm Jouppi 說道,他曾領導了谷歌的 TPU 項目。

與此同時,從事半導體研究的學術工作者對于未來的人工智能芯片有著自己的長遠設想。

現(xiàn)在,英特爾、Graphcore 和英偉達「已經在制造全刻線(full-reticle)芯片,下一步就是三維技術,」Patterson 說道,

「在摩爾定律當?shù)罆r,人們會比較排斥復雜的芯片封裝技術,對其可靠性和成本問題有所顧忌。現(xiàn)在摩爾定律已經終結了,芯片封裝領域將會出現(xiàn)很多其它的創(chuàng)新性實踐?!?

最終任務是創(chuàng)造新型的晶體管,使其可以堆疊在由邏輯和存儲器組成的裸片層上。

Suman Datta 是 Notre Dame 學院的一名電氣工程學教授,他認為負電容鐵電晶體管很適于創(chuàng)建這類芯片。

在最近一次有關所謂的單片 3D 架構的會議上,他談到了該領域的未來發(fā)展圖景。這種設計利用并提高了三維 NAND 閃存在芯片堆棧中的效益。

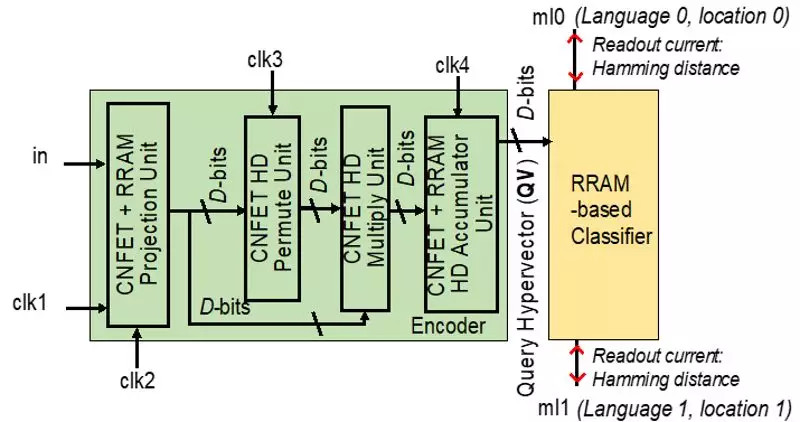

在今年 2 月舉行的國際固態(tài)電路會議(International Solid-State Circuits Conference)上,來自伯克利、麻省理工和斯坦福大學的一個團隊將提出一種體系架構,同樣富有遠見。

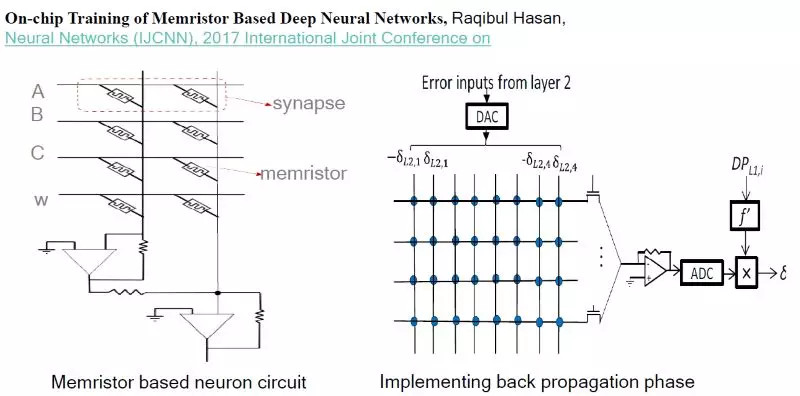

芯片(下圖)在帶有碳納米管制邏輯的裸片上,堆疊了電阻式 RAM(Resistive Random Access Memory,ReRAM)結構。

來自上述三校的研究人員將在 ISSCC 上介紹一種新型加速器,它使用碳納米管、ReRAM 以及模式作為計算元素

受深度神經網絡的啟發(fā),該裝置采用的是近似模式,而非計算機一直以來所使用的確切數(shù)字。

這個所謂的高維計算使用成千上萬維向量作為計算元素,伯克利教授 Jan Rabaey 說道,他也是該論文的貢獻者之一,并且是英特爾的智能咨詢委員會成員。

這種芯片可以從案例中進行學習,且其所需的操作次數(shù)遠遠少于傳統(tǒng)系統(tǒng),Rabaey 說。在一個關聯(lián)的內存陣列中,流片前的測試芯片將使用陣列振蕩器作為與 ReRAM 單元配對的模擬邏輯。

「我夢想中的引擎在場邊給我作指導…... 我的目標是把人工智能的操作能耗降低到 100 毫伏以下,」Rabaey 在 IEEE 人工智能研討會上說,

「我們需要重新思考我們的計算方式。我們的關注點正在從算法轉向基于數(shù)據(jù)的系統(tǒng)。」

2017-01-29 來源:36氪